Оперативная память

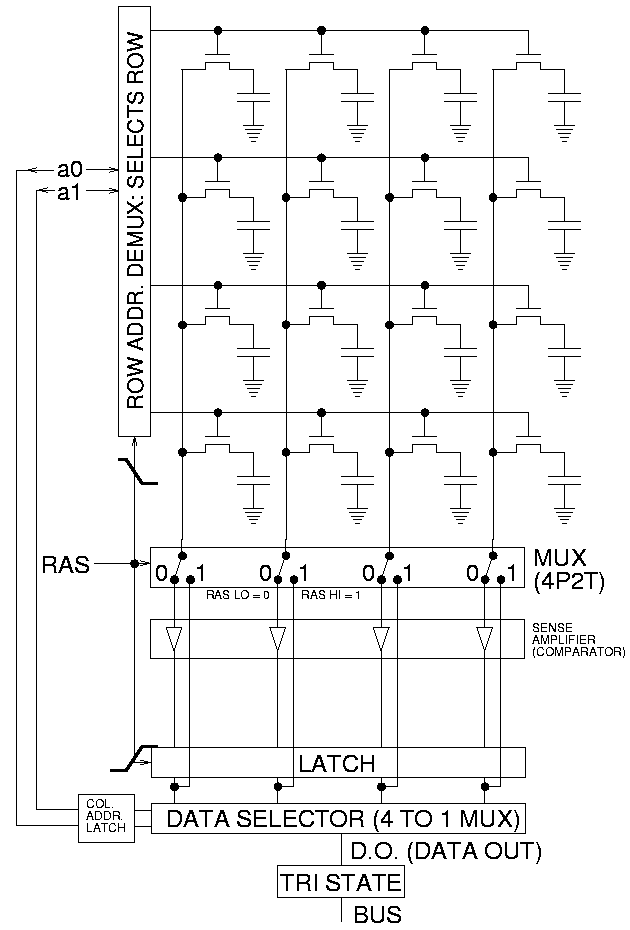

Оперативная память по большому счету представляет из себя простейшую логическую схему, обеспечивающую чтение-запись из адреса в памяти (раньше эта функциональность размещалась на северном мосте, сейчас чаще всего интегрированна на чип процессора) и банк триггеров. Банк триггеров физически расположен в виде двумерного массива и операции чтения-записи сводятся к

- Выобру ряда и его активации. При этом соотвествующий ряд подключается к выходам

- Работы непосредственно с рядом

Оперативная память характеризуется двумя основными показателями: частотой работы (измеряемой в герцах, i.e. количество циклов в секунду) и таймингами, определяющими количество циклов, необходимых для выполнения операции.

Типы памяти

Существует несколько технологий реализации триггеров в банках оперативной памяти. Два основных это “статический” и “динамический”. Статические триггеры принципиально похожи на RS-триггер, и достаточно дороги в производстве, но зато значительно быстрее динамических. Они обычно используются в качестве кэша процессора (объем кэша обычно в районе нескольких мегабайт). Динамические триггеры по сути представляют собой конденсатор. Основной их недостаток заключается в разрядке конденсатора, и, следовательно, необходимости постоянно перезаряжать конденсатор.

В соотвтетствии с типом триггера, оперативная память подразделяется на DRAM – динамическую и SRAM – статическую.

Динамическая память, в свою очередь, подразделяется на

- FPM DRAM

- Оригинальный тип динамическсокй памяти, читающий одну ячейку памяти за раз.

- EDO DRAM

- Не ожидая окончания чтения ячейки, как только выбраны ряд и столбец, переходит к поиску следующей. Примерно на 5% эффективнее, чем FPM, максимальная скорость чтения на 50% выше, чем у FPM

- SDRAM

- Не отключает ряд после чтения ячейки, что позволяет значительно ускорять операции последовательного чтения. Примерно на 5% эффективнее, чем EDO, максимальная скорость чтения на 100% выше.

- DDR SDRAM

- То же, что SDRAM, но совершает две операции за цикл. Позволяет увеличить вдвое эффективную частоту при прочих равных (ценой некоторого увеличения таймингов).

В современных компьютерах основным типом оперативной памяти является DDR SDRAM

Тайминги

Для 4 основных операций существуют 4 тайминга, а именно

- CL – CAS-latency, количество циклов, проходящих с передачи адреса до появления первого бита на выходах. Определяет скорость последовательного чтения

- RCD – Время включения ряда. Первичное чтение из произвольного ряда занимает RCD+CL циклов.

- RP – Время выключения ряда. Чтение из произвольного ряда со сменой ряда занимает RP+RCD+CL циклов

- RAS – Время, которое должно пройти между чтением/записью в ряд и переключением ряда. RCD+CL ≤ RAS ≤ RCD+2 CL

Тайминги обычно обозначаются тремя-четырьмя цифрами через дефис, например 6-6-6-24.